На прошедшем на прошлой неделе мероприятии Research@Intel Day компания Intel говорила о технологии, которая, возможно, позволит существенным образом повысить производительность будущих поколений процессоров.

Как известно, она определяется такими факторами как длина конвейера, число ядер, их частота и объём кэш-памяти. Тем не менее, не стоит забывать и об обмене данными между ядрами процессоров. Так, например, в 65-нм Kentsfield полоса пропускания составляет всего 8-9 ГБ/с, а в 45-нм чипах Harpertown — уже 18-20 ГБ/с.

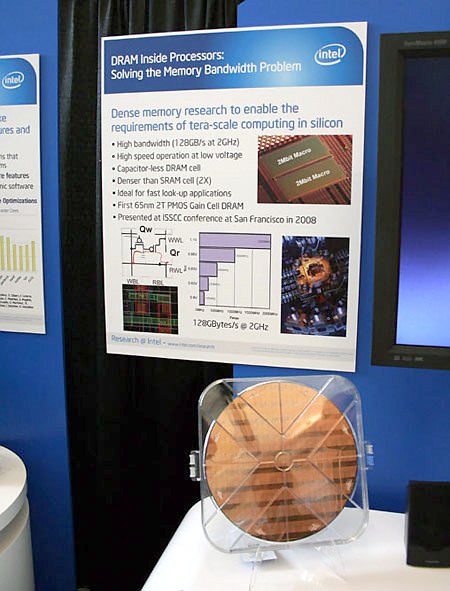

Именно за счёт внутренней пропускной полосы планируется поднять вычислительную мощь процессоров Intel. Небольшая команда исследователей компании в последнее время вела разработки технологии, которая бы позволила за счёт DRAM-памяти ускорить обмен данными внутри процессора с несколькими ядрами. Им удалось снизить размер ячеек DRAM до всего пары транзисторов и полностью избавиться от ёмкостей. Эти два шага и должны стать основополагающими в новой технологии. Вероятно, статическая память, сложная и дорогая, будет впоследствии полностью заменена в процессорах на динамическую.

В отличие от новой DRAM, требующей 2 транзистора для хранения 1 бита данных, у SRAM «расход» побольше — 6 транзисторов, а памяти 1T-SRAM в данных приложениях не нашла применения. Тем не менее, энергопотребление памяти SRAM несколько ниже, чем у DRAM, но это и стоит больше.

По данным компании, её инженерам удалось получить рабочие образцы 2T-DRAM-памяти, производимой по нормам 65 нм и работающей на частоте 2 ГГц. Полоса пропускания — впечатляющие 128 ГБ/с. Соответственно, если найти способ поднять частоту до уровня процессоров топ-класса (QX9770/9775), то это значение бы увеличилось до 204,8 ГБ/с. Это примерно в 10 раз более эффективное решение, чем использование сегодняшнего L2-кэш. Кроме того, такой подход полностью бы изменил и программирование под эти процессоры.

Ожидается, что благодаря 45-нм технологии High-k Intel удастся догнать по частоте процессоры и следующим логичным шагом может стать интеграция ячеек DRAM-памяти в процессоры Intel Terascale, в которых будет использоваться множество х86-ядер.

При сведении проблем с кэш-памятью практически к нулю (при низколатентной внутренней памяти с полосой пропускания около 200 ГБ/с) основная задача использования потенциала таких процессоров будет впоследствии возложена на программистов.